# **THE QUEST FOR LOW LATENCY STORAGE**

**Rick Coulson**

Senior Fellow, Intel NVM Solutions Group

#### Outline

- The history of storage latency and where we stand today

- The promise of Storage Class Memory (SCM) and 3D Xpoint<sup>™</sup> Memory

- Extensive compute platform changes driven by the quest for lower storage latency with SCM / 3D Xpoint<sup>™</sup> Memory

- As traditional storage

- As persistent memory

- Innovation opportunities abound

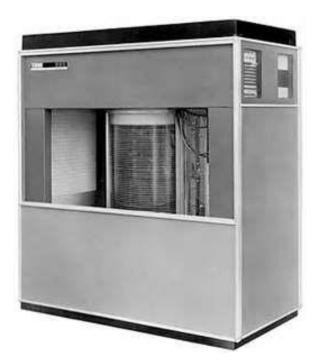

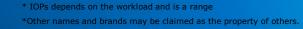

#### 1956: IBM RAMAC 350

5 MBytes

\$57,000

\$15200/Mbyte

~1.5 Random IOPs\*

<u>600ms latency</u>

Now-

"SINGLE STEP" DATA PROCESSING FOR SMALLER BUSINESSES with

IBM's RAMAC

With these whirling magnetic disks, RAMAC gives you a 5-million character memory ... an unprecedented system whereby your millions of buriness facts and figures can be stored economically, in a random monner, and yet be immediately accessible!

RAMAC is the first all purpose, chectronic accounting system designed comparely in one unit. , first to make "single step" data processing available to the smaller business? By single step processing we mean RAMAC's abitry to process transactions at they occars, while at the same time updating all related side, inventory and billing records. With RAMAC your facts-on-file are forever current

For all its compact, cost-saving size, RAMAC easily handles your many accounting, record-keeping and manufacturing control problems.

Learn the many ways IBM's new RAMAC can profit your company. Just call your local IBM representative.

> IBM DATA PROCESSING

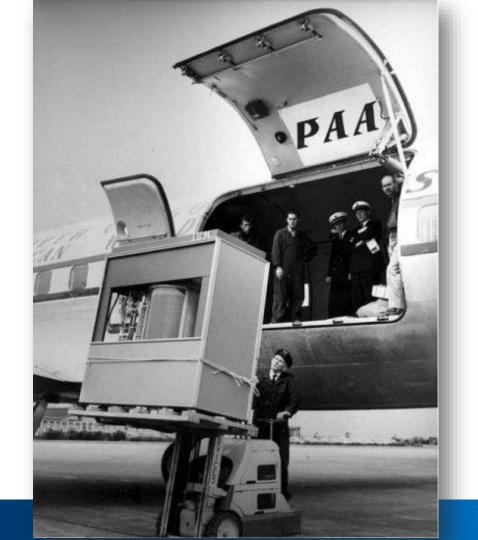

# 300 Mbytes

1980: IBM 3350

\$60,000

\$200/MByte

30 random IOPs

<u>33ms latency</u>

#### 1983: IBM3380

2.52 GBytes \$82,000 \$36/MByte ~160 IOPS total <u>25ms latency</u>

Two hard disk assemblies each with two independent actuators each accessing 630 MB gigabyte within one chassis

#### 2007: 15K RPM HDD

#### 15K RPM HDD

About 200 random IOPs\*

~5ms latency

#### IOPS scaling problem was addressed through HDDs in parallel in Enterprise

\* IOPs depends on the workload and is a range

#### 2016: 10K RPM HDD

1.8TB

~150 IOPs

<u>6.6ms latency</u>

#### 2016 NVMe NAND SSD

**2TB**

500,000+ IOPs

~60 usec latency

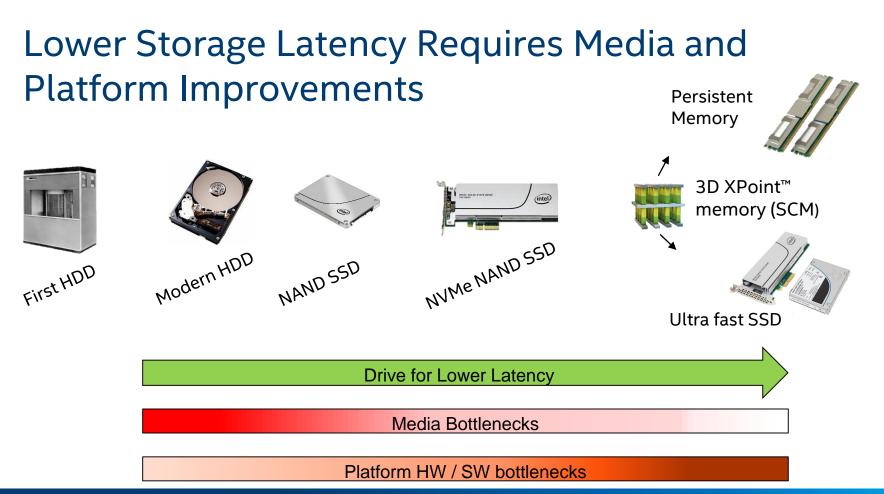

### The Continuing Need For Lower Latency

# Addressing Media Latency: Next Gen NVM / SCM

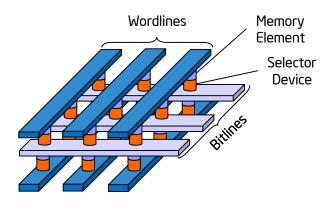

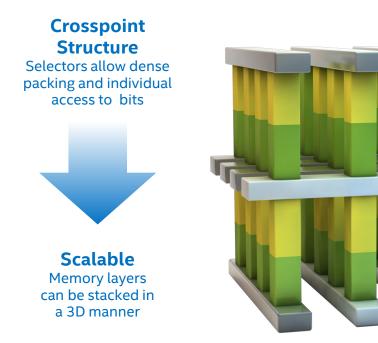

#### Scalable Resistive Memory Element

Cross Point Array in Backend Layers  ${\sim}4\lambda^2$  Cell

#### **Resistive RAM NVM Options**

| Family                                  | Defining Switching<br>Characteristics                                                                          |

|-----------------------------------------|----------------------------------------------------------------------------------------------------------------|

| Phase<br>Change<br>Memory               | Energy (heat) converts material<br>between crystalline (conductive) and<br>amorphous (resistive) <u>phases</u> |

| Magnetic<br>Tunnel<br>Junction<br>(MTJ) | Switching of magnetic resistive<br>layer by <u>spin-polarized electrons</u>                                    |

| Electrochemical<br>Cells (ECM)          | Formation / dissolution of<br>"nano-bridge" by <u>electrochemistry</u>                                         |

| Binary Oxide<br>Filament<br>Cells       | Reversible filament formation by<br>Oxidation-Reduction                                                        |

| Interfacial<br>Switching                | Oxygen vacancy drift diffusion induced barrier modulation                                                      |

#### Scalable, with potential for near DRAM access times

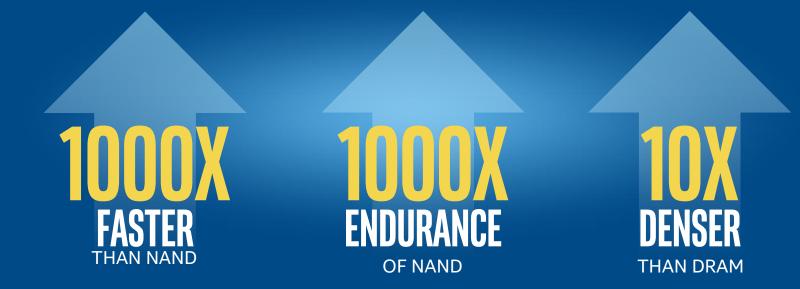

### 3D XPoint<sup>™</sup> Technology

Breakthrough Material Advances Compatible switch and memory cell materials

High Performance Cell and array architecture that can switch states 1000x faster than NAND

# **A NEW CLASS OF NON-VOLATILE MEMORY**

\*Results have been estimated or simulated using internal analysis or architecture simulation or modeling, and provided to you for informational purposes. Any differences in your system hardware, software or configuration may affect your actual performance

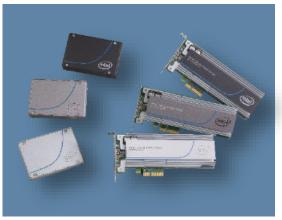

#### 3D XPoint<sup>™</sup> Technology Instantiation

#### INTEL<sup>®</sup> OPTANE<sup>™</sup> SSDS

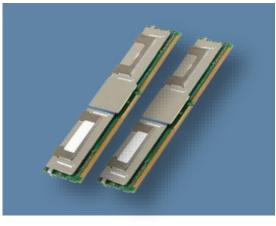

#### DIMMS BASED ON 3D XPOINT<sup>™</sup>

# 3D Xpoint<sup>™</sup> Technology Video

Please excuse the marketing

#### 3D Xpoint<sup>™</sup> Technology Video

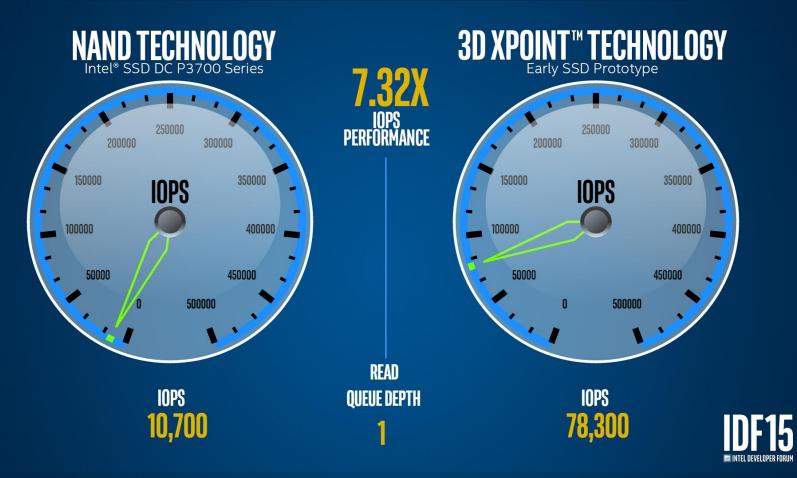

#### Demonstration of 3D Xpoint<sup>™</sup> SSD Prototype

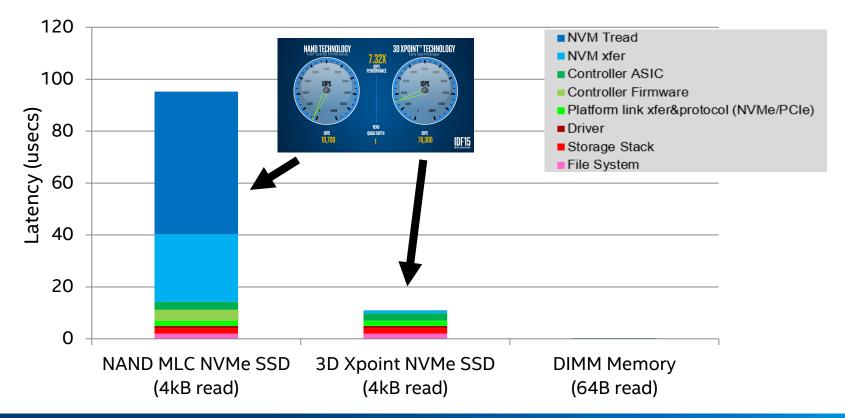

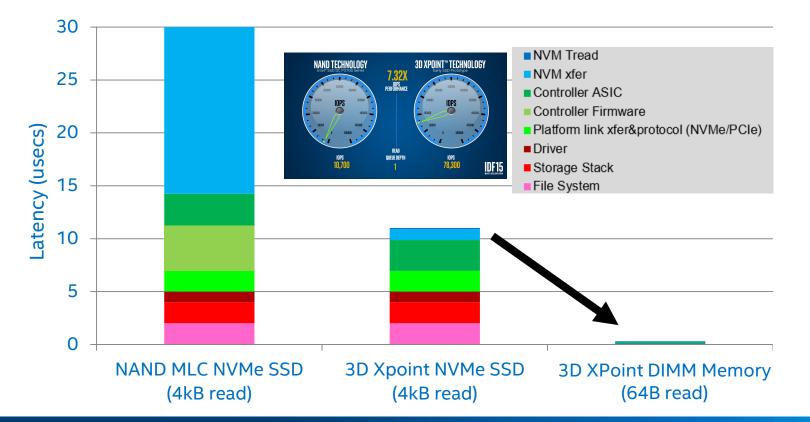

#### Need to Address System Architecture To Go Lower

#### **Block Storage Platform Changes**

#### INTEL<sup>®</sup> OPTANE<sup>™</sup> SSDS

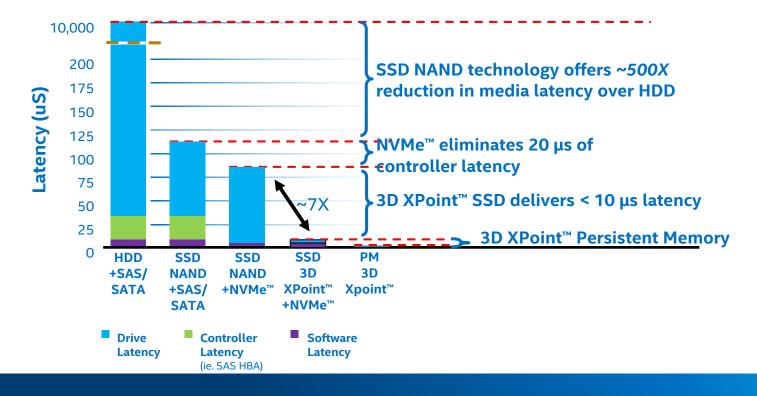

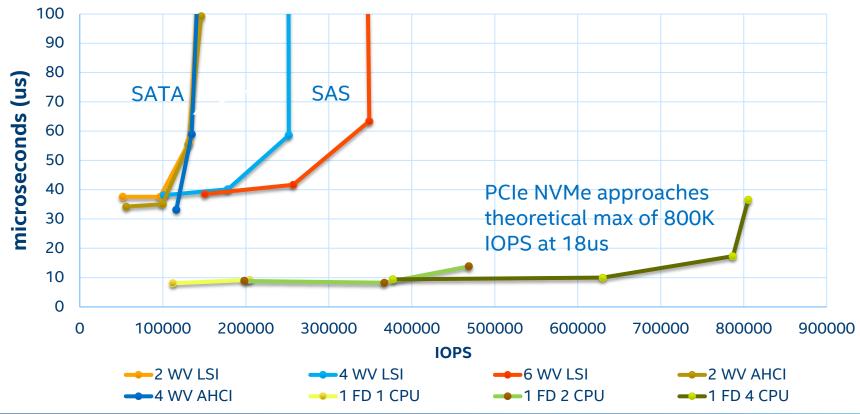

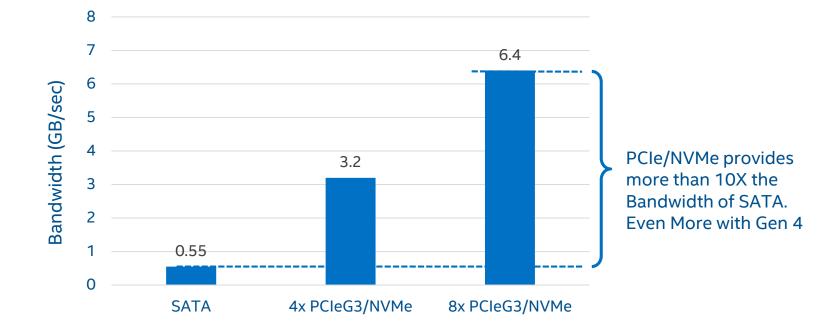

### Addressing Interface Efficiency With NVMe / PCI

### **NVMe Delivers Superior Latency**

Platform HW/SW Average Latency Excluding Media 4KB

#### NVMe/PCIe Provides More Bandwidth

### **Storage SW Stack Optimizations**

Much of the storage stack designed with HDDs latencies in mind

- No point in optimizing until now

- Example: Paging algorithms with seek optimization and grouping

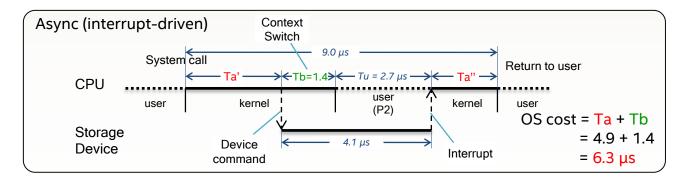

# Synchronous Completion for Queue Depth 1?

From Yang: FAST '12 -10th USENIX Conference on File and Storage Technologies

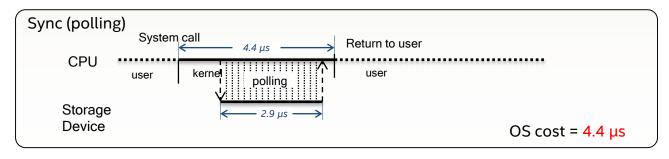

### Standards for Low Latency Replication

In most Datacenter usage models, a storage write does not "count" until replicated

High replication overhead diminishes the performance differentiation of 3D XPoint<sup>™</sup> technology

NVMe over Fabrics is a developing SNIA specification for low overhead replication

### Summary: Block Storage Platform Changes

Move to PCIe based storage

Streamlined command set NVMexpress

OS / SW stack optimizations

Fast replication standards

#### INTEL<sup>®</sup> OPTANE<sup>™</sup> SSDS

#### Persistent Memory Oriented Platform Changes

#### DIMMS BASED ON 3D XPOINT<sup>™</sup>

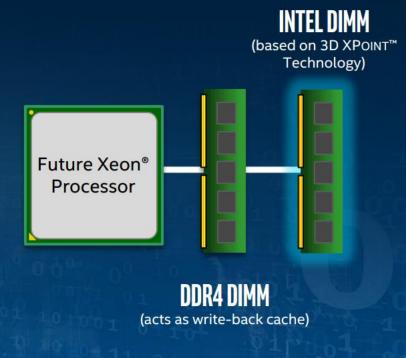

# **INTEL DIMMS** Based on 3D XPoint™ Technology

- DDR4 electrical & physical compatible

- Required support delivered by next generation Intel<sup>®</sup> Xeon<sup>®</sup> platform

- Up to 4X system memory capacity, at significantly lower cost than DRAM

DATA CENTER DAY

Can deliver big memory benefits without modifications to OS or applications

# Why Persistent Memory?

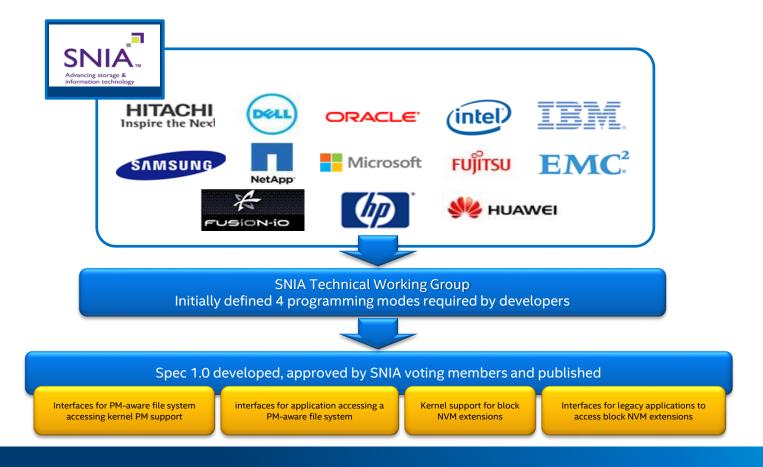

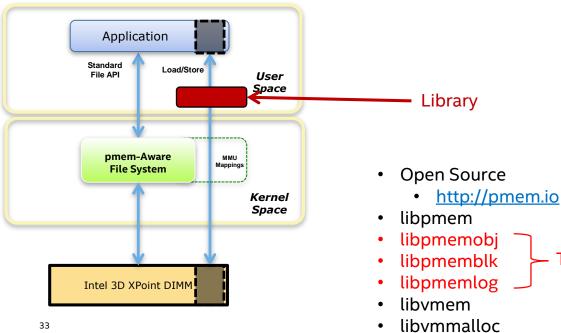

### **Open NVM Programming Model**

# NVM Library: pmem.io

64-bit Linux Initially

**Transactional**

33

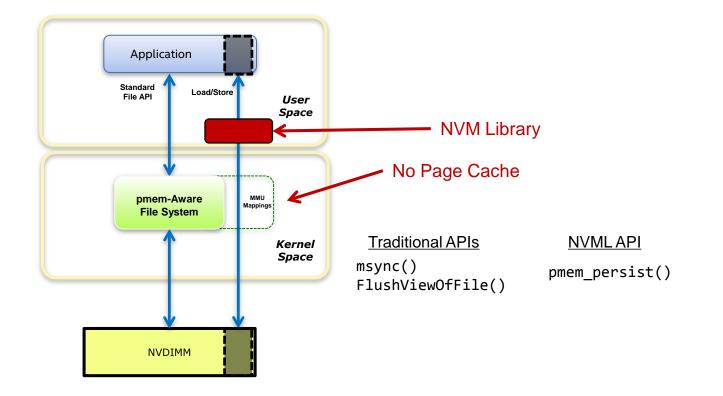

#### Write I/O Replaced with *Persist Points*

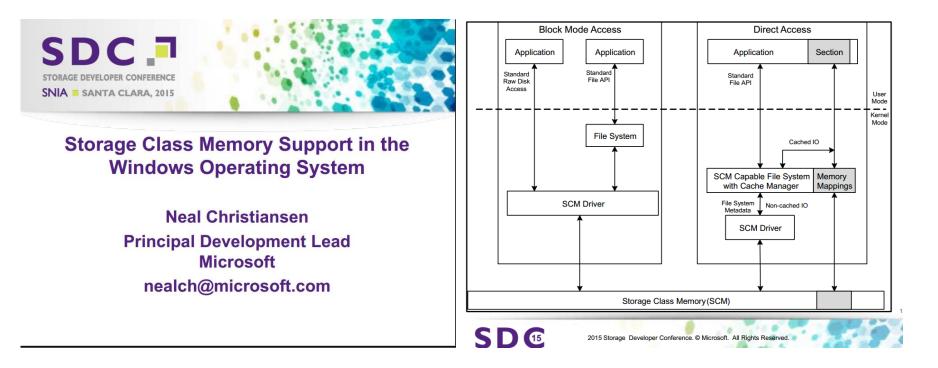

### **Operating System Support for Persistent Memory**

#### The Data Path

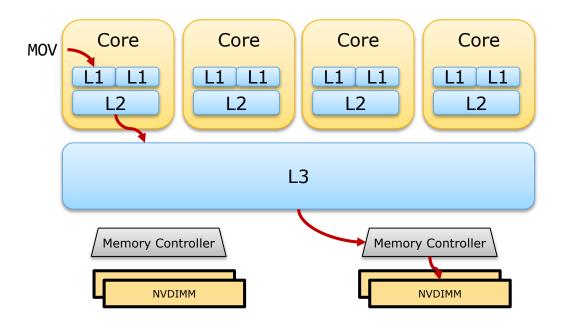

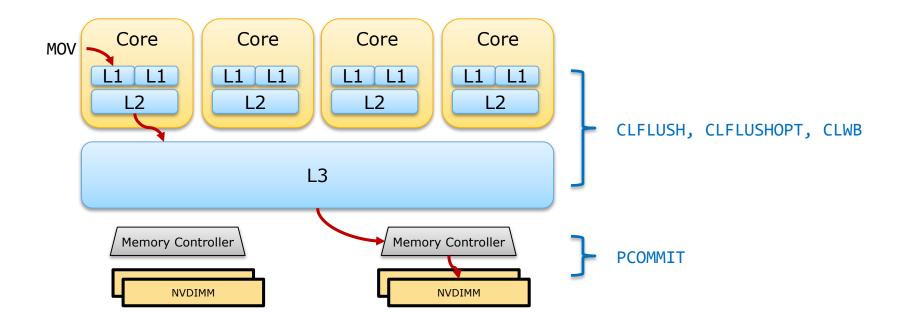

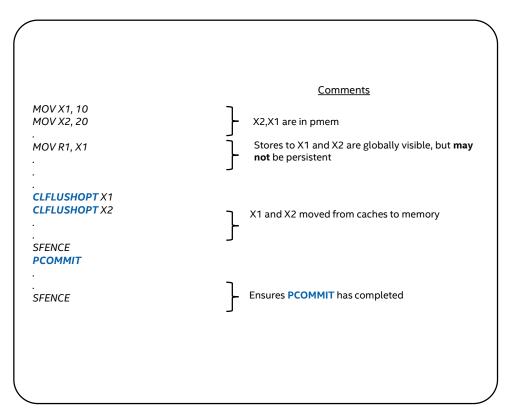

#### New Instructions For Flushing Writes

### Flushing Writes from Caches

| Instruction     | Meaning                                                                          |

|-----------------|----------------------------------------------------------------------------------|

| CLFLUSH addr    | Cache Line Flush:<br>Available for a long time                                   |

| CLFLUSHOPT addr | Optimized Cache Line Flush:<br>New to allow concurrency                          |

| CLWB addr       | Cache Line Write Back:<br>Leave value in cache<br>for performance of next access |

#### Flushing Writes from Memory Controller

| Instruction               | Meaning                                                                   |

|---------------------------|---------------------------------------------------------------------------|

| PCOMMIT                   | Persistent Commit:<br>Flush stores accepted by<br>memory subsystem        |

| Asynchronous DRAM Refresh | Flush outstanding writes<br>on power failure<br>Platform-Specific Feature |

#### Example Code

# Join the Discussion about Persistent Memory

#### Learn about the Persistent Memory programming model

http://www.snia.org/forums/sssi/nvmp

#### Join the pmem NVM Libraries Open Source project

http://pmem.io

#### Read the documents and code supporting ACPI 6.0 and Linux NFIT drivers

- http://www.uefi.org/sites/default/files/resources/ACPI\_6.0.pdf

- https://git.kernel.org/cgit/linux/kernel/git/djbw/nvdimm.git/log/?h=nd

- <u>https://github.com/pmem/ndctl</u>

- <u>http://pmem.io/documents/</u>

- https://github.com/01org/prd

#### Intel Architecture Instruction Set Extensions Programming Reference

https://software.intel.com/en-us/intel-isa-extensions

Intel 3D XPoint<sup>™</sup> Memory

http://www.intel.com/content/www/us/en/architecture-and-technology/non-volatile-memory.html

### **Persistent Memory Summary**

New storage model for low latency

New instructions to support persistence

**OS support**

Lots of innovation opportunity

#### DIMMS BASED ON 3D XPOINT<sup>™</sup>

# Low Latency Ahead <1 usec Persistent Memory (intel) 3D XPoint<sup>™</sup> memory NVMe SSD <10 usec Ultra fast SSD