# TIME TRAVELING HARDWARE AND SOFTWARE SYSTEMS

Xiangyao Yu, Srini Devadas CSAIL, MIT

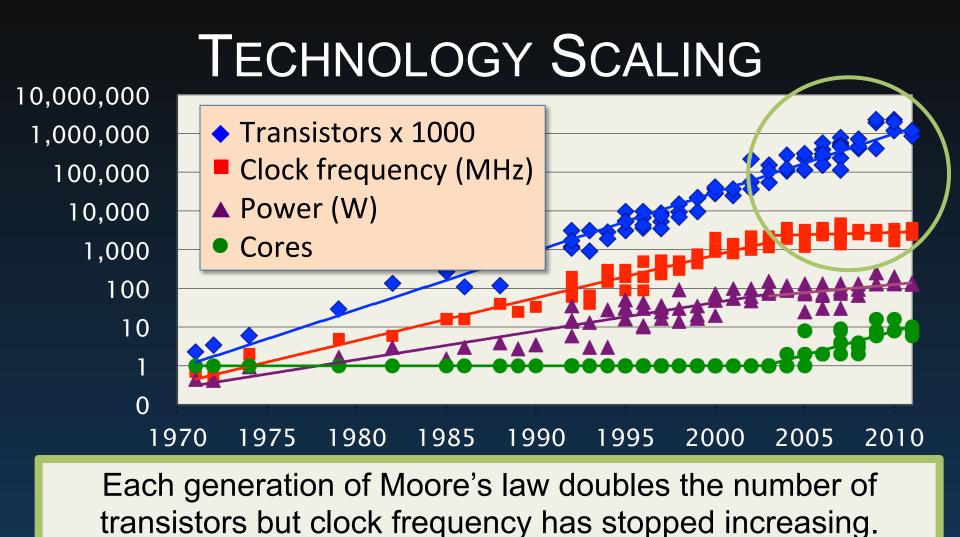

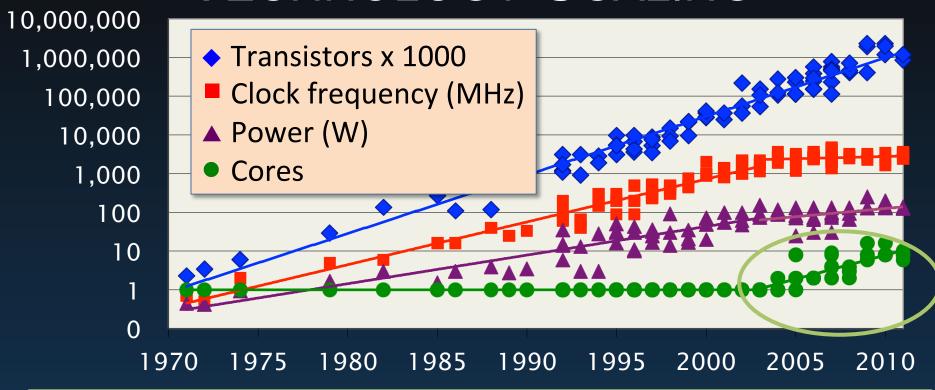

# FOR FIFTY YEARS, WE HAVE RIDDEN MOORE'S LAW

Moore's Law and the scaling of clock frequency = printing press for the currency of performance

### TECHNOLOGY SCALING

To increase performance, need to exploit parallelism.

# DIFFERENT KINDS OF PARALLELISM - 1

#### **Instruction Level**

$$a = b + c$$

$d = e + f$

$g = d + b$

#### **Transaction Level**

Read A

Read B

Compute C

Read A

Read D

Compute E

Read C Read E Compute F

# DIFFERENT KINDS OF PARALLELISM - 2

#### **Thread Level**

Different thread computes each entry of product matrix C

#### Task Level

Search("image")

Cloud

# DIFFERENT KINDS OF PARALLELISM - 3

#### Thread Level

Different thread computes each entry of product matrix C

#### **User Level**

Query("record")

# DEPENDENCY DESTROYS PARALLELISM

Need to compute i<sup>th</sup> entry after i - 1<sup>th</sup> has been computed ⊗

# DIFFERENT KINDS OF DEPENDENCY

Read A No Read A dependency! Write A

Write A

WAW: Semantics decide order

Write A Read A RAW: Read needs new value

Read A Write A WAR: We have flexibility here!

# DEPENDENCE IS ACROSS TIME, BUT WHAT IS TIME?

- Time can be physical time

- Time could correspond to logical timestamps assigned to instructions

- Time could be a combination of the above

→ Time is a definition of ordering

#### WAR DEPENDENCE

```

Initially A = 10

Thread 0

Thread 1

Write A ...... A=13

Order

Physical Time

Order

Corder

Local copy of A = 10

```

Read happens later than Write in physical time but is before Write in logical time.

#### WHAT IS CORRECTNESS?

We define correctness of a parallel program based on its outputs in relation to the program run sequentially

### SEQUENTIAL CONSISTENCY

Global Memory Order

Can we exploit this freedom in correct execution to avoid dependency?

# AVOIDING DEPENDENCY ACROSS THE STACK

| ا<br>ا<br>ا | Circuit                      | Efficient atomic instructions                                  |

|-------------|------------------------------|----------------------------------------------------------------|

|             | Multicore<br>Processor       | Tardis coherence protocol                                      |

|             | Multicore<br>Database        | TicToc concurrency control  with Andy Pavlo and Daniel Sanchez |

| r<br>D<br>D | Distributed Database         | Distributed TicToc                                             |

|             | Distributed<br>Shared Memory | Transaction processing with fault tolerance                    |

### SHARED MEMORY SYSTEMS

Multi-core Processor

OLTP Database

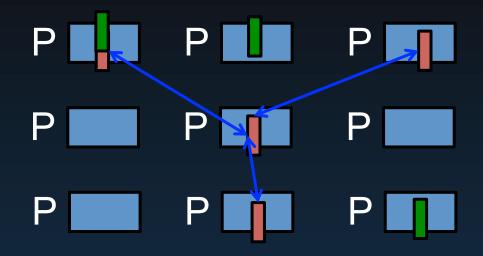

### DIRECTORY-BASED COHERENCE

- Data replicated and cached locally for access

- Uncached data copied to local cache, writes invalidate data copies

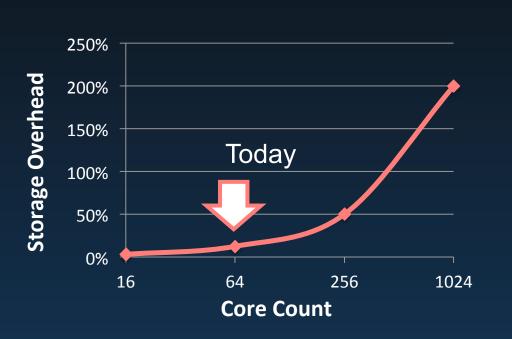

#### CACHE COHERENCE SCALABILITY

### LEASE-BASED COHERENCE

- A read gets a lease on a cacheline

- Lease renewal after lease expires

- A store can only commit after leases expire

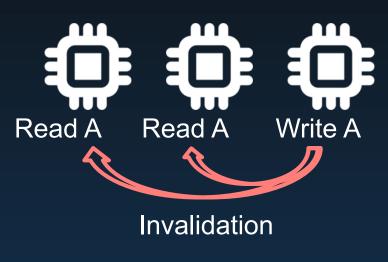

- Tardis: logical leases

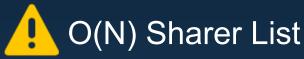

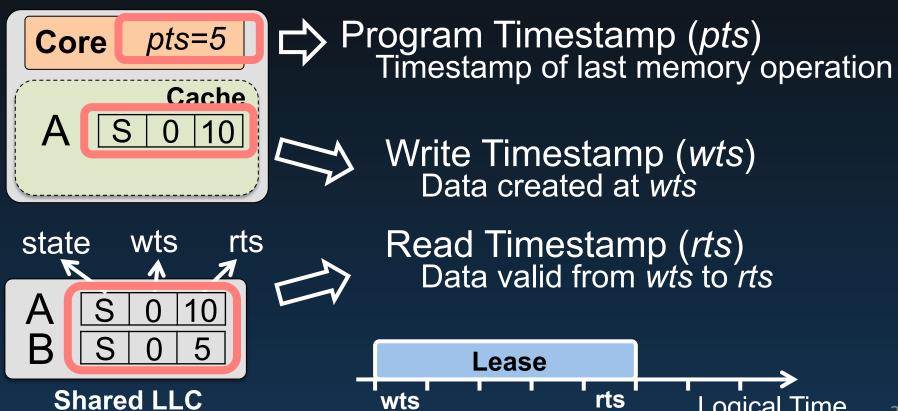

#### LOGICAL TIMESTAMP

Physical Time Order Invalidation Logical Time Order **Tardis** (concept borrowed from database) (No Invalidation) **Old Version New Version** logical time

#### TIMESTAMP MANAGEMENT

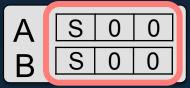

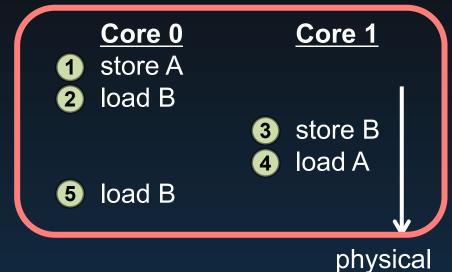

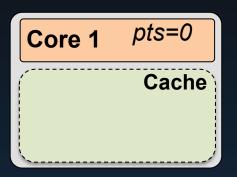

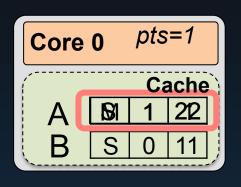

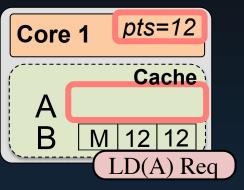

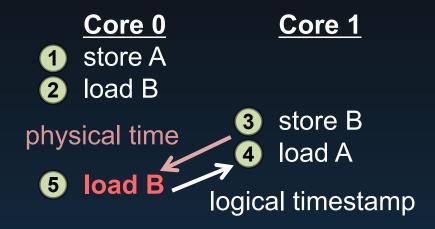

### TWO-CORE EXAMPLE

time

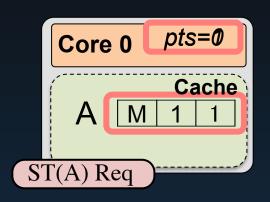

## STORE A @ CORE 0

- Core 0

- Core 1 store A

- load B

- store B

- load A

load B

Write at pts = 1

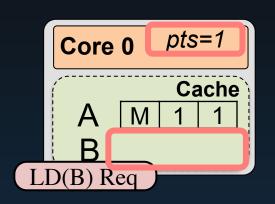

## LOAD B @ CORE 0

Core 1

2 load B

- 3 store B

- 4 load A

6 load B

Reserve rts to pts + lease = 11

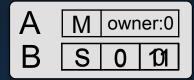

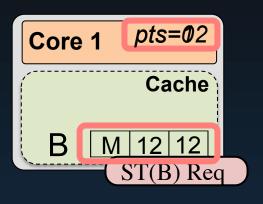

## STORE B @ CORE 1

- Core 0

- 1 store A

- 2 load B

6 load B

Core 1

- 3 store B

- 4 load A

Exclusive ownership returned No invalidation

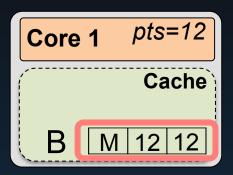

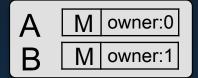

#### Two Versions Coexist

1 store A

2 load B

3 store B

Core 1

4 load A

5 load B

Core 1 traveled ahead in time Versions ordered in logical time

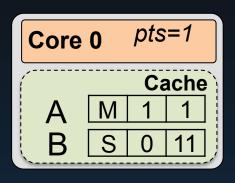

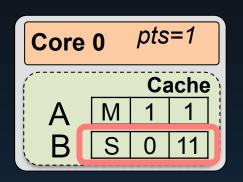

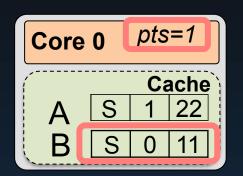

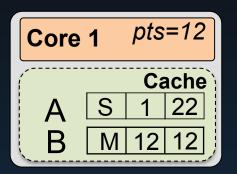

## LOAD A @ CORE 1

- Core 0

- 1 store A

- 2 load B

3 store B

Core 1

4 load A

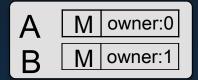

WB(A) Req

A M owner:1

Write back request to Core 0

load B

Downgrade from M to S

Reserve rts to pts + lease = 22

## LOAD B @ CORE 0

global memory order ≠ physical time order

### SUMMARY OF EXAMPLE

physical time order

physical + logical time order

### Physiological Time

$$X <_{PL} Y := X <_{L} Y \text{ or } (X =_{L} Y \text{ and } X <_{P} Y)$$

Thm: Tardis obeys Sequential Consistency

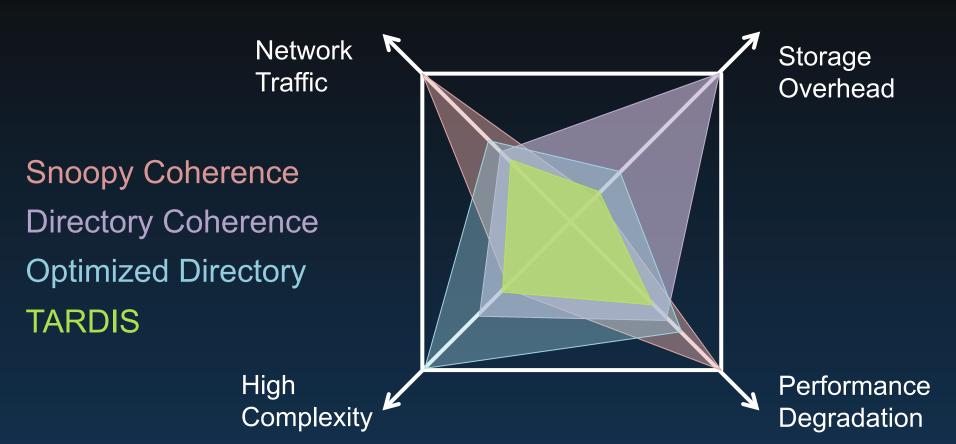

### TARDIS PROS AND CONS

Scalability

No Invalidation, Multicast or Broadcast

#### **EVALUATION**

#### Storage overhead per cacheline (N cores)

Directory: **N** bits per cacheline

Tardis: Max(Const, log(N)) bits per cacheline

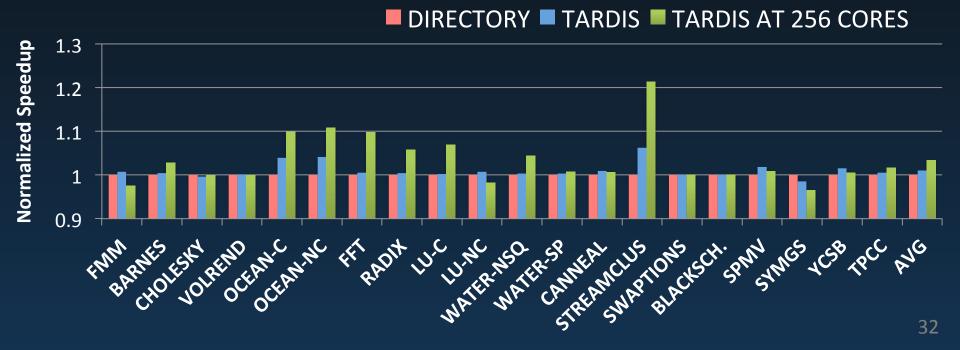

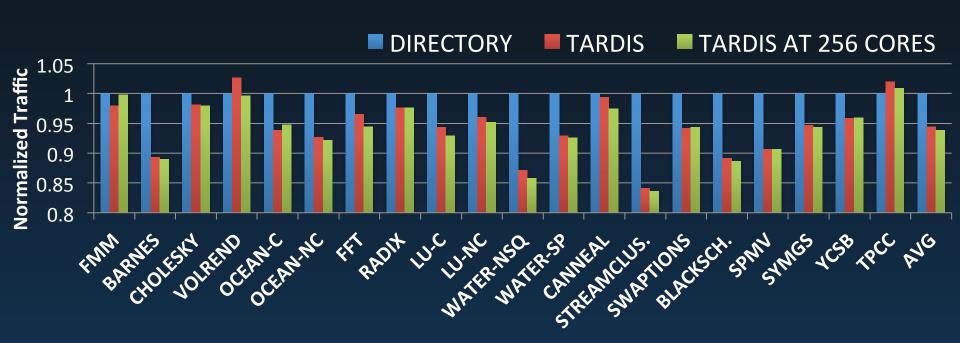

#### SPEEDUP

#### Graphite Multi-core Simulator (64 cores)

### NETWORK TRAFFIC

#### CONCURRENCY CONTROL

Serializability

Results should correspond to some serial order of atomic execution

### CONCURRENCY CONTROL

#### Can't Have This

Results should correspond to some serial order of atomic execution

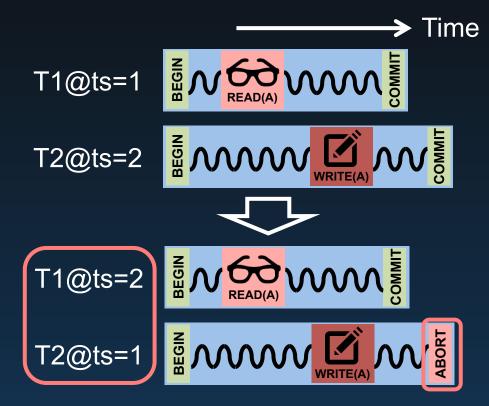

## BOTTLENECK 1: TIMESTAMP ALLOCATION

- Centralized Allocator

- Timestamp allocation is a scalability bottleneck

- Synchronized Clock

- Clock skew causes unnecessary aborts

## BOTTLENECK 2: STATIC ASSIGNMENT

- Timestamps assigned before a transaction starts

- Suboptimal assignment leads to unnecessary aborts.

#### KEY IDEA: DATA DRIVEN TIMESTAMP MANAGEMENT

#### Traditional T/O

- 1. Acquire timestamp (TS)

- Determine tuple visibility using TS

- Timestamp Allocation

- Static Timestamp Assignment

#### TicToc

- 1. Access tuples and remember their timestamp info.

- 2. Compute commit timestamp (CommitTS)

- No Timestamp Allocation

- Dynamic Timestamp Assignment

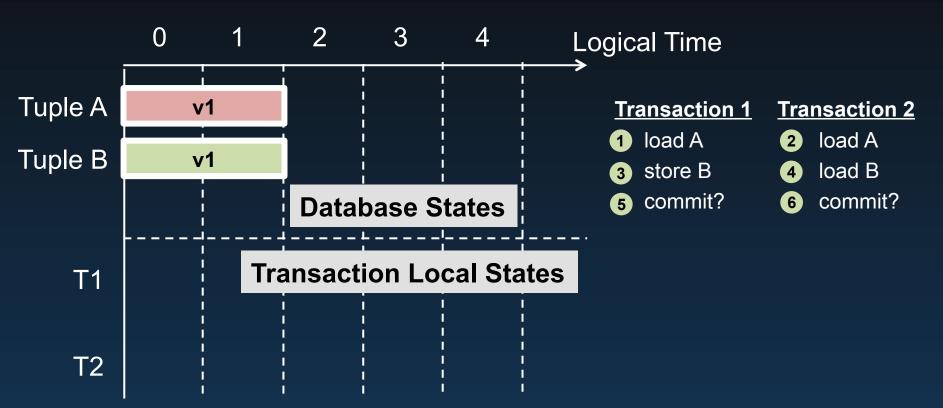

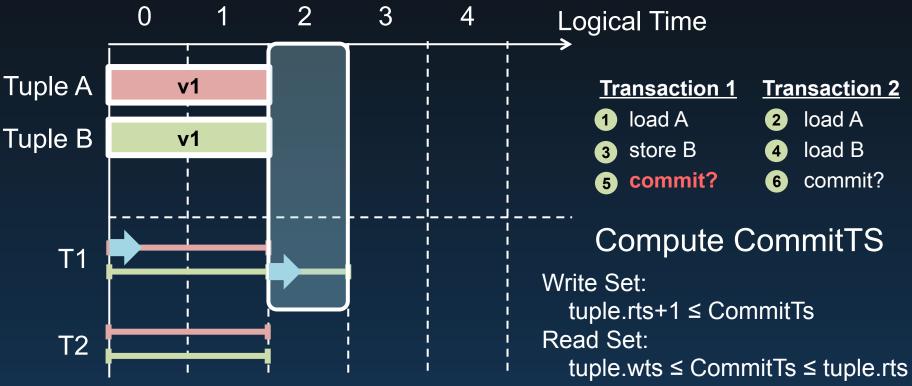

## TICTOC TRANSACTION EXECUTION

Read & Write Tuples Execute Transaction

- Compute CommitTS

- Decide Commit/Abort

Update Database

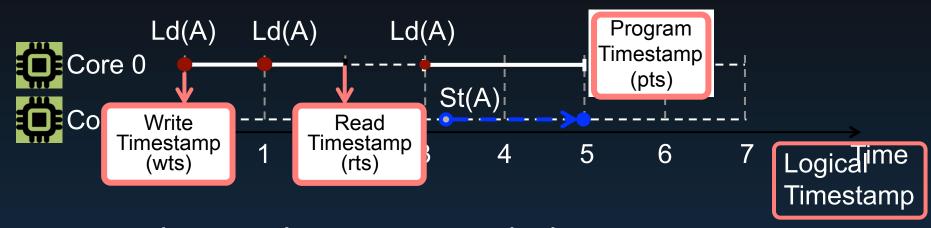

wts: last data write @ wts

rts: last data read @ rts

data valid between wts and rts

Tuple Format

**Data**

wts (Write Timestamp) rts (Read Timestamp)

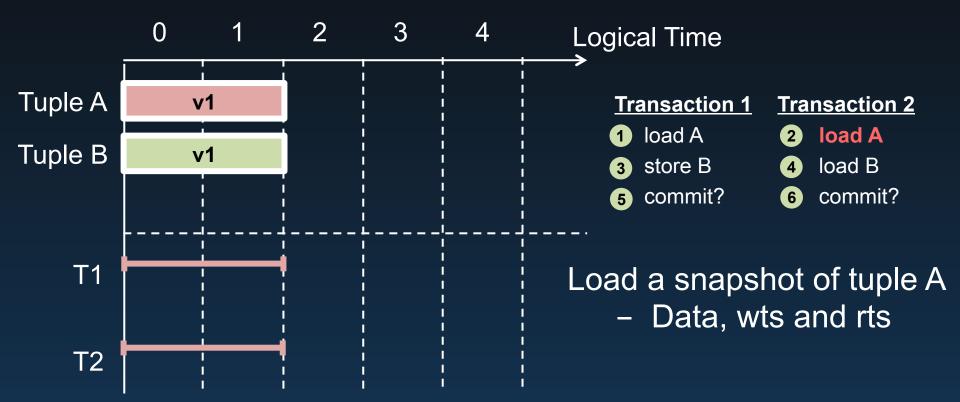

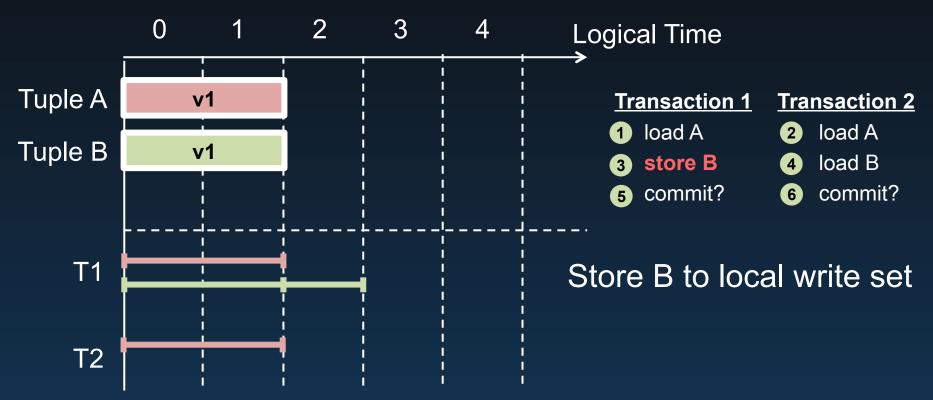

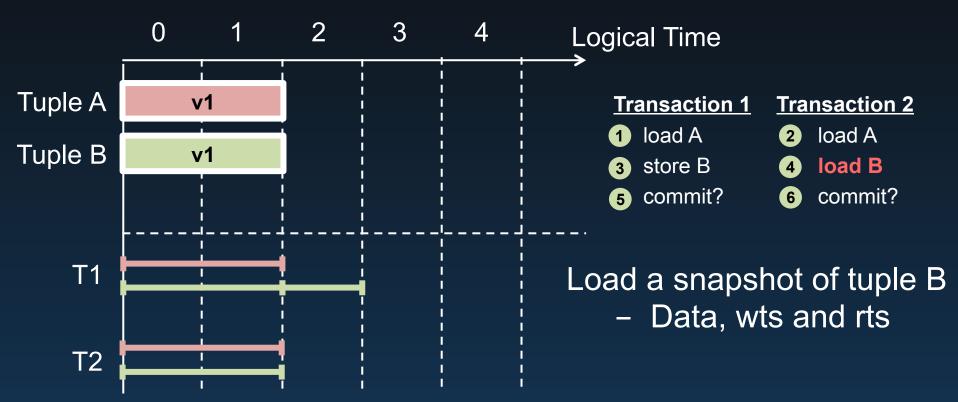

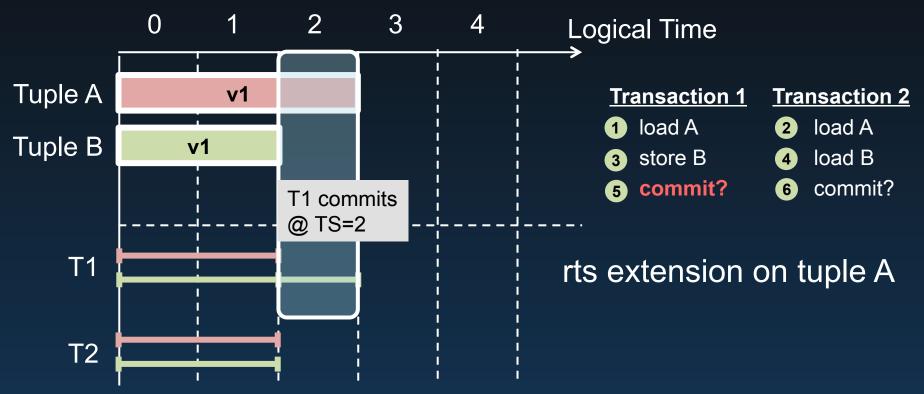

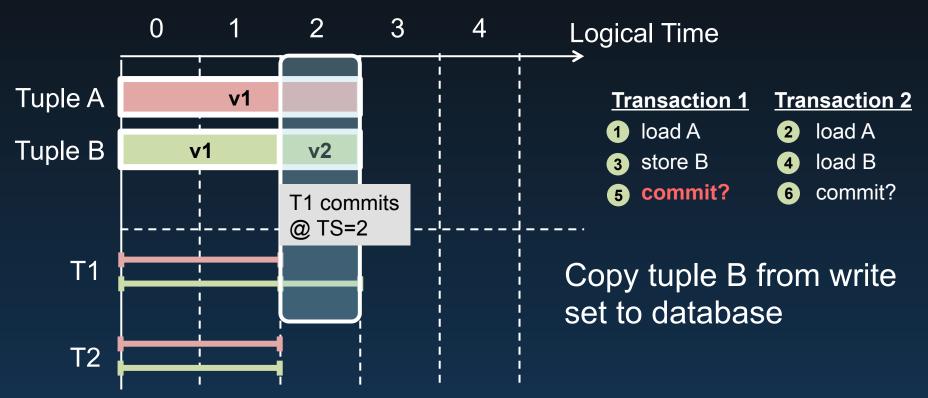

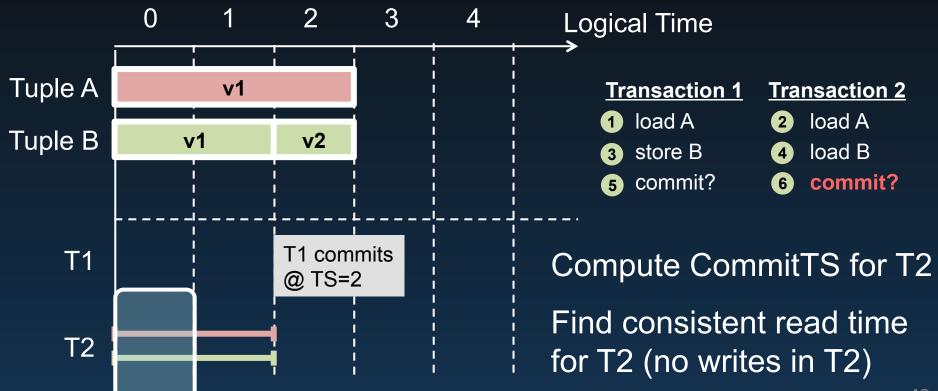

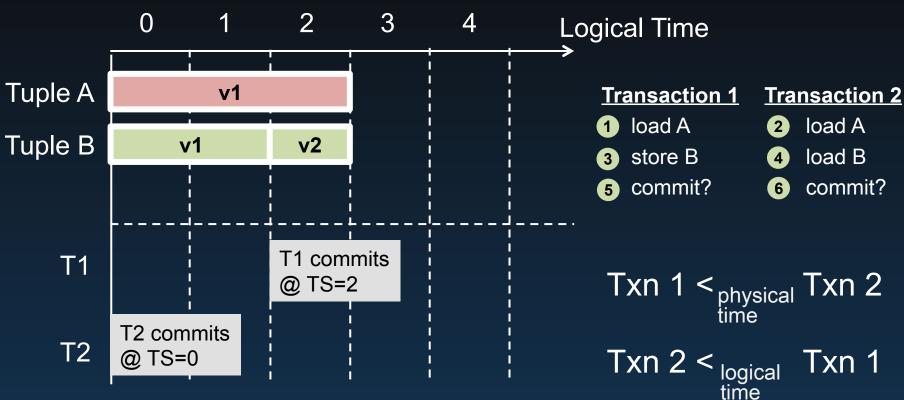

#### TICTOC EXAMPLE

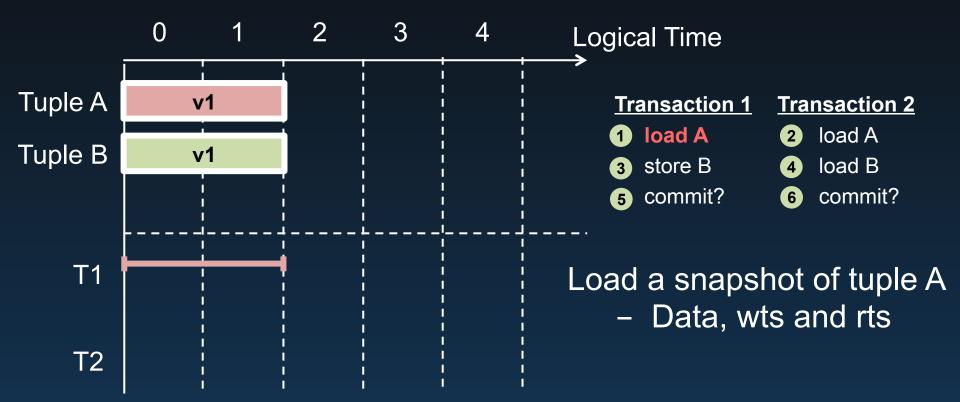

#### LOAD A FROM T1

#### LOAD A FROM T2

#### STORE B FROM T1

#### LOAD B FROM T2

### FINAL STATE

Thm: Serializability = All operations valid at CommitTS

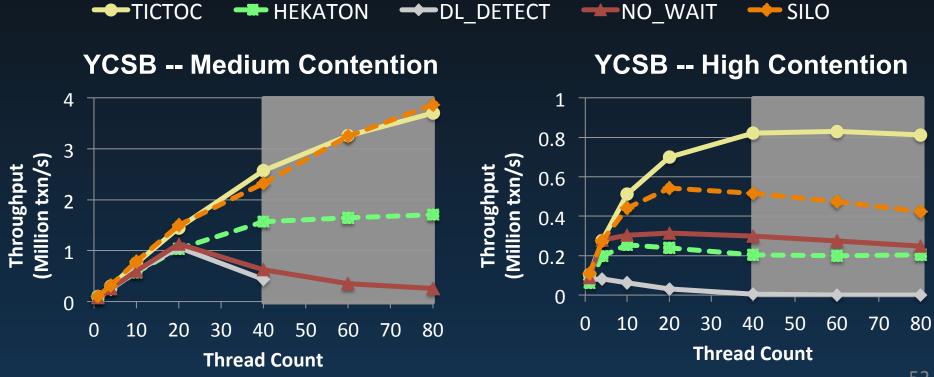

#### EXPERIMENTAL SETUP

- DBx1000: Main Memory DBMS

- No logging

- No B-tree (hash indexing)

- Concurrency Control Algorithms

- MVCC: HEKATON (Microsoft)

- OCC: SILO (Harvard/MIT)

- 2PL: DL\_DETECT, NO\_WAIT

- 10 GB YCSB Benchmark

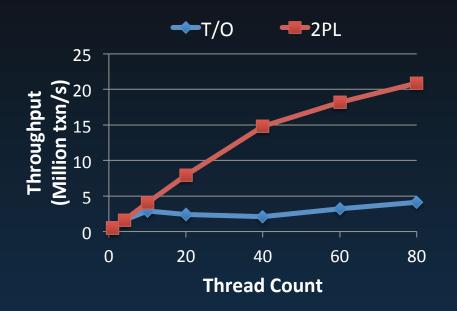

#### EVALUATION

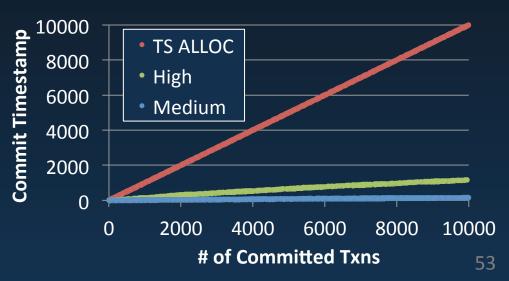

#### TICTOC DISCUSSION

Thm: Serializability = All ops valid at CommitTS

Transactions may have same CommitTS

Logical timestamp growing rate indicates inherent parallelism

# PHYSIOLOGICAL TIME ACROSS THE STACK

| <u>ي ا</u> ا | Circuit                   | Efficient atomic instructions               |

|--------------|---------------------------|---------------------------------------------|

|              | Multicore<br>Processor    | Tardis coherence protocol                   |

|              | Multicore<br>Database     | TicToc concurrency control                  |

| rŌ1<br>ŌŌ    | Distributed<br>Database   | Distributed TicToc                          |

|              | Distributed Shared Memory | Transaction processing with fault tolerance |

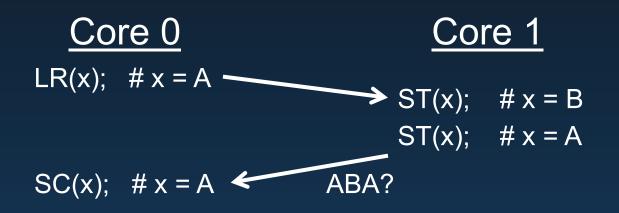

## ATOMIC INSTRUCTION (LR/SC)

- ABA Problem

- Detect ABA using timestamp (wts)

#### TARDIS CACHE COHERENCE

- Simple: No Invalidation

- Scalable:

- O(log N) storage

- No Broadcast, No Multicast

- No Clock Synchronization

- Support Relaxed Consistency Models

# T1000: PROPOSED 1000-CORE SHARED MEMORY PROCESSOR

#### TICTOC CONCURRENCY CONTROL

- Data Driven Timestamp Management

- No Central Timestamp Allocation

- Dynamic Timestamp Assignment

#### DISTRIBUTED TICTOC

- Data Driven Timestamp Management

- Efficient Two-Phase Commit Protocol

- Support Local Caching of Remote Data

## FAULT TOLERANT DISTRIBUTED SHARED MEMORY

- Transactional Programming Model

- Distributed Command Logging

- Dynamic Dependency Tracking Among

Transactions (WAR dependency can be ignored)

# TIME TRAVELING TO ELIMINATE WAR

Xiangyao Yu, Srini Devadas CSAIL, MIT